Intel GG8067401635553 Ficha de datos Pagina 239

- Pagina / 608

- Tabla de contenidos

- MARCADORES

Valorado. / 5. Basado en revisión del cliente

Gigabit LAN Configuration Registers

Intel® Xeon® Processor D-1500 Product Family 239

Datasheet - Volume 1 of 4: Integrated Platform Controller Hub

March 2015

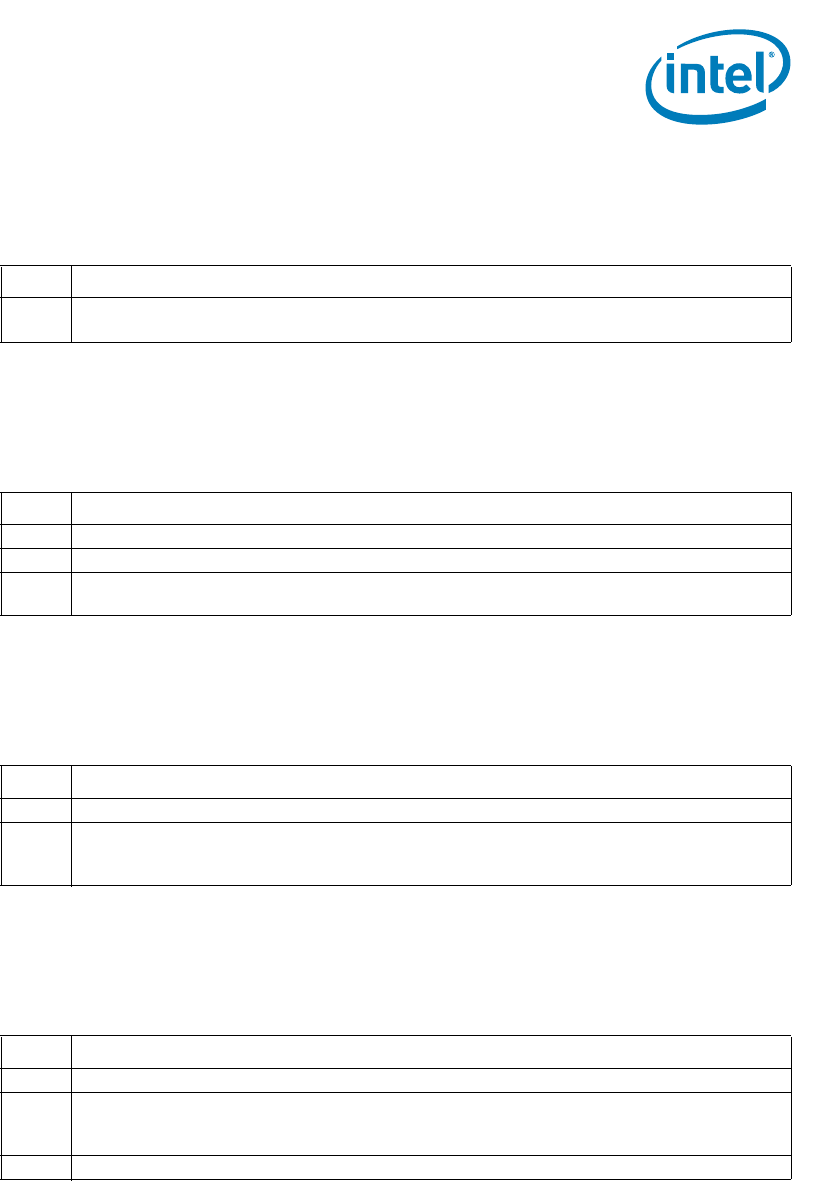

6.2.7 GBECSR_5400—Gigabit Ethernet Capabilities and Status

Register 5400

Address Offset: MBARA + 5400h Attribute: R/W

Default Value: XXXXXXXXh Size: 32 bits

6.2.8 GBECSR_5404—Gigabit Ethernet Capabilities and Status

Register 5404

Address Offset: MBARA + 5404h Attribute: R/W

Default Value: XXXXXXXXh Size: 32 bits

6.2.9 GBECSR_5800—Gigabit Ethernet Capabilities and Status

Register 5800

Address Offset: MBARA + 5800h Attribute: R/W/SN

Default Value: 00000008h Size: 32 bits

6.2.10 GBECSR_5B54—Gigabit Ethernet Capabilities and Status

Register 5B54

Address Offset: MBARA + 5B54h Attribute: RO

Default Value: 60000040h Size: 32 bits

Bit Description

31:0 Receive Address Low (RAL)— R/W.

The lower 32 bits of the 48 bit Ethernet Address.

Bit Description

31 Address Valid— R/W.

30:16 Reserved

15:0 Receive Address High (RAH)— R/W.

The lower 16 bits of the 48 bit Ethernet Address.

Bit Description

31:1 Reserved

0 Advanced Power Management Enable (APME) — R/W/SN.

1 = APM Wakeup is enabled

0 = APM Wakeup is disabled

Bit Description

31:16 Reserved

15 Firmware Valid Bit (FWVAL) — RO.

1 = Firmware is ready

0 = Firmware is not ready

14:0 Reserved

- Product Family 1

- March 2015 10

- Revision History 21

- 1 Introduction 24

- 1.1.1 Chapter Descriptions 25

- 1.2 Overview 26

- 1.2.1 Capability Overview 27

- Controller) 28

- Gigabit Ethernet Controller 29

- Enhanced Power Management 30

- Manageability 30

- Introduction 31

- Integrated Chipset Definition 32

- 2 Intel® Xeon® Processor D 35

- Table 2-1. SoC Clock Inputs 36

- Table 2-2. Clock Outputs 36

- 2.3 Functional Blocks 37

- ME) Control 38

- Enable Register 40

- Attribute: R/W 41

- 3 Functional Description 49

- 3.2.2 Interrupt Generation 50

- 3.2.3 Power Management 51

- 3.2.4 SERR# Generation 52

- 3.2.5 Hot-Plug 53

- 3.2.5.4 SMI/SCI Generation 54

- 3.3.1.1 Transaction Layer 57

- 3.3.1.2 Data Alignment 57

- 3.3.2.1 Data Parity Error 57

- 3.3.3 Ethernet Interface 58

- 3.3.4 PCI Power Management 58

- 3.3.5 Configurable LEDs 60

- 3.3.6.1 FLR Steps 61

- 3.4.1 LPC Interface 62

- 3.4.1.1 LPC Cycle Types 63

- 3.4.1.4 Size 64

- 3.4.1.5 SYNC 65

- 3.4.1.6 SYNC Time-Out 65

- 3.4.1.7 SYNC Error Indication 65

- 3.4.1.8 LFRAME# Usage 65

- 3.5 DMA Operation (D31:F0) 67

- 3.5.1 Channel Priority 68

- 3.5.4 Autoinitialize 69

- 3.6 Low Pin Count (LPC) DMA 70

- 3.6.2 Abandoning DMA Requests 71

- 3.6.4 Terminal Count 72

- 3.6.5 Verify Mode 72

- 3.7 8254 Timers (D31:F0) 74

- 3.7.2.1 Simple Read 76

- 3.7.2.2 Counter Latch Command 76

- 3.7.2.3 Read Back Command 76

- 3.8.1 Interrupt Handling 78

- 3.8.2.1 ICW1 79

- 3.8.2.2 ICW2 79

- 3.8.2.3 ICW3 79

- 3.8.4 Modes of Operation 80

- 3.8.4.5 Poll Mode 81

- 3.8.5 Masking Interrupts 82

- (APIC) (D31:F0) 83

- 3.9.2 Interrupt Mapping 84

- 3.10.1 Start Frame 86

- 3.10.2 Data Frames 86

- 3.10.3 Stop Frame 87

- 3.10.5 Data Frame Format 87

- 3.11 Real Time Clock (D31:F0) 88

- 3.11.1 Update Cycles 89

- 3.11.2 Interrupts 89

- 3.11.3 Lockable RAM Ranges 89

- 3.11.4 Century Rollover 89

- Using RTCRST# to Clear CMOS 90

- 3.12 Power Management 91

- System Power States 92

- 3.12.3 System Power Planes 93

- 3.12.4 SMI# / SCI Generation 94

- 3.12.4.1 PCI Express* SCI 96

- 3.12.5 C-States 97

- 3.12.6 Sleep States 97

- 3.12.6.3 Exiting Sleep States 98

- Sleep Button 101

- 3.12.7.2 RI# (Ring Indicator) 101

- 3.12.7.4 SYS_RESET# Signal 102

- 3.12.7.5 THRMTRIP# Signal 102

- 3.12.8 ALT Access Mode 103

- 3.12.8.2 PIC Reserved Bits 105

- 3.12.9.3 PCH_PWROK Signal 106

- SLP_S4#, SLP_A# and SLP_LAN# 106

- Functional Description 107

- March 2015 107

- 3.12.9.7 RTCRST# and SRTCRST# 109

- 3.12.11 Reset Behavior 110

- 3.13.1 Theory of Operation 112

- 3.13.1.2 Handling an Intruder 113

- 3.13.2 TCO Modes 114

- 3.13.2.2 Advanced TCO Mode 115

- 3.14.1 Power Wells 116

- 3.14.3 Triggering 116

- 3.14.5.1 Theory of Operation 117

- Internal Clock 119

- Manchester D 119

- Bit 7 0123456 119

- 3.15.1 SATA 6 Gb/s Support 120

- 3.15.2 SATA Feature Support 120

- 3.15.3 Theory of Operation 121

- 3.15.4 SATA Swap Bay Support 121

- 3.15.5 Hot-Plug Operation 122

- 3.15.8 SATA Device Presence 124

- 3.15.9 SATA LED 125

- 3.15.10 AHCI Operation 125

- 3.15.11 SGPIO Signals 126

- 3.15.11.2 Message Format 127

- 3.15.11.3 LED Message Type 127

- 3.15.11.4 SGPIO Waveform 129

- 3.16.1 Timer Accuracy 130

- 3.16.2 Interrupt Mapping 130

- Non-Periodic Mode 131

- Periodic Mode 131

- 3.16.4 Enabling the Timers 132

- 3.16.5 Interrupt Levels 132

- 3.16.6 Handling Interrupts 133

- 3.17.1 EHC Initialization 134

- 3.17.5 Packet Formats 135

- 3.17.7.1 Pause Feature 136

- 3.17.7.2 Suspend Feature 136

- 3.17.7.3 ACPI Device States 136

- 3.17.7.4 ACPI System States 137

- 3.17.9.1 Theory of Operation 138

- Behavioral Rules 138

- Enabling the Debug Port 141

- Determining the Debug Port 141

- 3.17.10 EHCI Caching 142

- 3.17.11 Intel 142

- USB Pre-Fetch Based Pause 142

- 3.17.12.1 FLR Steps 143

- 3.18.1 Overview 144

- 3.18.2 Architecture 144

- 3.19 xHCI Controller (D20:F0) 145

- 3.20.1 Host Controller 146

- Block Read/Write 148

- 3.20.2 Bus Arbitration 150

- 3.20.3 Bus Timing 151

- 3.20.4 Interrupts / SMI# 151

- 3.20.5 SMBALERT# 152

- 3.20.7 SMBus Slave Interface 152

- 3.21 Thermal Management 158

- Throttling 160

- Interface (SMLink0) 161

- 3.21.3.2 Block Read Command 162

- 3.21.3.3 Read Data Format 162

- 3.21.3.6 BIOS Set Up 163

- 3.21.3.7 SMBus Rules 164

- 3.22.1 Intel 167

- Management Engine (Intel 167

- ME) Requirements 167

- 3.23.1.1 Non-Descriptor Mode 169

- 3.23.1.2 Descriptor Mode 169

- 3.23.2 Flash Descriptor 170

- 3.23.3 Flash Access 172

- 3.23.9 PWM Outputs 179

- 3.23.10 TACH Inputs 179

- 3.25 Intel 180

- Product Family IOxAPIC 181

- 4 Register and Memory Mapping 182

- 4.1 PCI Devices and Functions 183

- 4.2 PCI Configuration Map 184

- 4.3 I/O Map 184

- (Sheet 2 of 3) 185

- 4.4 Memory Map 187

- Register and Memory Mapping 190

- Express* Root Ports Register 192

- SMI# for software to read 194

- 1E18–1E1Fh Attribute: RO 195

- 201A–201Bh Attribute: RO 196

- 2026–2027h Attribute: RO 196

- 2320–2323h Attribute: R/W 197

- 3000h Attribute: R/W 197

- 20AC–20AFh Attribute: R/W 197

- 2314–2317h Attribute: R/W 197

- 3104–3107h Attribute: RO 198

- 3108–310Bh Attribute: R/W 198

- 310C–310Fh Attribute: R/W 199

- 3110–3113h Attribute: R/W 200

- 3114–3117h Attribute: R/W 200

- 3118–311Bh Attribute: R/W 200

- 3124–3127h Attribute: R/W 201

- 3128–312bh Attribute: R/W 201

- 3140–3141h Attribute: R/W 201

- 3142–3143h Attribute: RO 202

- 3144–3145h Attribute: R/W 202

- 3146–3147h Attribute: R/W 203

- 3148–3149h Attribute: R/W 204

- 314C–314Dh Attribute: R/W 205

- 3150–3151h Attribute: R/W 206

- 315C–315Dh Attribute: R/W 207

- 3160–3161h Attribute: R/W 207

- 31FE–31FFh Attribute: R/W 208

- 3300–3303h Attribute: R/W 209

- 3304–3307h Attribute: R/W 209

- Register 210

- 3314–3317h Attribute: R/W 211

- 3318–331Bh Attribute: R/W 211

- 3324–3327h Attribute: R/W 212

- 3340–3343h Attribute: R/W 213

- 3344–3347h Attribute: R/W 213

- 3348–334Bh Attribute: R/W 213

- 3350–3353h Attribute: R/W 213

- 33A0–33A3h Attribute: R/W 215

- 33B0–33B3h Attribute: R/W 215

- 33C0–33C3h Attribute: R/W 215

- 33C8–33CBh Attribute: R/W 215

- 33D0–33D3h Attribute: R/W 215

- 33D4–33D7h Attribute: R/W 216

- 3404–3407h Attribute: R/W 216

- (yy = xx0000x0b) 217

- 3414h Attribute: R/W 218

- 3418–341Bh Attribute: R/W 219

- 341C–341Fh Attribute: R/W 220

- F0–F3h Attribute: R/W 224

- 6 Gigabit LAN Configuration 225

- (Sheet 2 of 2) 226

- 06h–07h Attribute: R/WC, RO 227

- 08h Attribute: RO 228

- 09h–0Bh Attribute: RO 228

- 0Ch Attribute: R/W 228

- 0Dh Attribute: RO 228

- 0Eh Attribute: RO 228

- 10h–13h Attribute: R/W, RO 229

- 14h–17h Attribute: R/W, RO 229

- 18h–1Bh Attribute: R/W, RO 229

- 2Ch–2Dh Attribute: RO 230

- 2Eh–2Fh Attribute: RO 230

- 30h–33h Attribute: RO 230

- 34h Attribute: RO 230

- 3Ch–3Dh Attribute: R/W, RO 230

- 3Eh–3Fh Attribute: RO 231

- A0h–A3h Attribute: RO 231

- A4h–A7h Attribute: RO 231

- A8h–ABh Attribute: R/W 231

- (Gigabit LAN—D25:F0) 232

- Register (Gigabit LAN—D25:F0) 233

- D0h–D1h Attribute: R/WO, RO 234

- D2h–D3h Attribute: R/W, RO 234

- D4h–D7h Attribute: R/W 234

- D8h–dBh Attribute: R/W 234

- DCh–DDh Attribute: R/W 235

- E0h–E1h Attribute: RO 235

- E2h–E3h Attribute: R/WO, RO 235

- E4–E5h Attribute: R/W 236

- MBARA + 00h Attribute: R/W 237

- MBARA + 20h Attribute: R/W/V 237

- MBARA + 2Ch Attribute: R/W 238

- MBARA + 5400h Attribute: R/W 239

- MBARA + 5404h Attribute: R/W 239

- MBARA + 5B54h Attribute: RO 239

- (D31:F0) 240

- 00h–01h Attribute: RO 241

- 02h–03h Attribute: RO 241

- 04h–05h Attribute: R/W, RO 241

- Lockable: No Power Well: Core 242

- 2Ch–2Fh Attribute: R/WO 244

- 40h–43h Attribute: R/W, RO 244

- 44h Attribute: R/W 244

- Bit Description 244

- 48h–4Bh Attribute: R/W, RO 245

- 4Ch Attribute: R/W 245

- (LPC I/F—D31:F0) 246

- 6Ch–6Dh Attribute: R/W 248

- H0BDF 70h–71h 248

- Power Well: Core 249

- 88h–8Bh Attribute: R/W 251

- 8Ch–8Eh Attribute: R/W 251

- 90h–93h Attribute: R/W 251

- D4h–D5h Attribute: R/W 254

- D8h–D9h Attribute: R/W, RO 254

- E2h Attribute: RO 257

- E3h Attribute: RO 257

- E4h–E7h Attribute: R/W 257

- 7.1.39 Feature Vector Space 258

- 7.2 DMA I/O Registers 259

- 7.3 Timer I/O Registers 265

- RdBK_CMD—Read Back Command 266

- Table 7-3. PIC Registers 268

- 4D0h Attribute: R/W 273

- 4D1h Attribute: R/W 273

- 7.5.1 APIC Register Map 274

- 7.5.2 IND—Index Register 275

- 7.5.3 DAT—Data Register 275

- 7.5.4 EOIR—EOI Register 275

- 7.5.6 VER—Version Register 276

- 32 bit quantities) 277

- 7.6 Real Time Clock Registers 278

- 7.6.2 Indexed Registers 279

- RTC Index: 0Bh Attribute: R/W 280

- Lockable: No Power Well: RTC 280

- 7.7.3 PORT92—Init Register 283

- Power Well: RTC, SUS 287

- A9h Attribute: R/W 290

- AAh Attribute: R/W, RO 290

- ABh Attribute: R/W, RO 290

- B8h–BBh Attribute: R/W 291

- BCh–BFh Attribute: R/W 291

- 7.8.2 APM I/O Decode Register 292

- TCO Register I/O Map 307

- (Except Bit 0, in RTC) 309

- TCOBASE + 0Eh Attribute: R/W 312

- TCOBASE + 10h Attribute: R/W 312

- GPIOBASE +04h Attribute: R/W 314

- GPIOBASE +0Ch Attribute: R/W 314

- Resume for 8:15, 24:31 315

- Status Register 316

- GPIOBASE +24h Attribute: R/W 317

- GPIOBASE +28h Attribute: R/W 317

- GPIOBASE +2Ch Attribute: R/W 318

- GPIOBASE +30h Attribute: R/W 318

- GPIOBASE +34h Attribute: R/W 319

- GPIOBASE +38h Attribute: R/W 319

- GPIOBASE +40h Attribute: R/W 319

- GPIOBASE +44h Attribute: R/W 320

- GPIOBASE +48h Attribute: R/W 320

- GPIOBASE +60h Attribute: R/W 321

- GPIOBASE +64h Attribute: R/W 321

- 8 SATA Controller Registers 323

- 04h–05h Attribute: RO, R/W 325

- 1Ch–1Fh Attribute: R/W, RO 328

- 8.1.16.1 When SCC is not 01h 329

- 8.1.16.2 When SCC is 01h 330

- 3Ch Attribute: R/W 331

- 3Dh Attribute: RO 331

- 3100h:bits 11:8) 331

- 48h Attribute: R/W 332

- 4Ah–4Bh Attribute: R/W 332

- 54h–57h Attribute: R/W 332

- 70h–71h Attribute: RO 333

- 72h–73h Attribute: RO 333

- 74h–75h Attribute: R/W, R/WC 333

- Register (SATA–D31:F2) 334

- Function Level Reset: No 337

- 8.1.37.1 339

- (SATA–D31:F2) 341

- E8h–EBh Attribute: R/W 344

- Register (D31:F2) 346

- SIDPBA + 00h Attribute: R/W 347

- SIDPBA + 04h Attribute: R/W 347

- Register 347

- Address Offset: Attribute: RO 348

- Attribute: R/WC 349

- 8.4 AHCI Registers (D31:F2) 350

- Function Level Reset:No 351

- ABAR + 10h–13h Attribute: RO 355

- ABAR + 1Ch–1Fh Attribute: RO 355

- 8.4.2 Port Registers (D31:F2) 356

- Mnemonic Register 358

- 9 SATA Controller Registers 371

- When SCC = 01h 374

- (SATA–D31:F5) 376

- Register (SATA–D31:F5) 380

- 92h–93h Attribute: R/W, RO 381

- B2h–B3h Attribute: RO, R/WO 383

- B4h–B5h Attribute: R/W, RO 383

- C0h Attribute: R/W 383

- C4h Attribute: R/WC 383

- Secondary: BAR + 08h 384

- Secondary: BAR + 0Ah 385

- Register (D31:F5) 386

- Attribute: R/W, RO 388

- 10 EHCI Controller Registers 391

- 09h Attribute: RO 394

- 0Ah Attribute: RO 394

- 0Bh Attribute: RO 395

- 2Ch–2Dh Attribute: R/W 396

- 2Eh–2Fh Attribute: R/W 396

- Register (USB EHCI—D29:F0) 398

- 62–63h Attribute: R/W, RO 400

- 64h Attribute: R/W, RO 401

- 66h Attribute: R/W, RO 401

- 68–6Bh Attribute: R/W, RO 401

- Power Well: Suspend 402

- 10.1.31 SPECIAL_SMI—Intel 403

- (USB EHCI—D29:F0) 403

- Bit: 31 30 29 28 27 26 25 24 404

- Port: X X XX3210 404

- Bit: 23 22 21 20 19 18 17 16 404

- Bit: 15 14 13 12 11 10 9 8 405

- Bit: 7 6 543210 405

- 84h Attribute: R/W 406

- 98h Attribute: RO 406

- 99h Attribute: RO 406

- 9Ah–9Bh Attribute: R/WO, RO 407

- 9Ch Attribute: R/W 407

- 9Dh Attribute: RO 407

- MEM_BASE + 00h Attribute: RO 408

- • Suspend well hardware reset 411

- • HCRESET 411

- Attribute: R/W, R/WC, RO 417

- Power well: Suspend 420

- 11 xHCI Controller Registers 423

- 14h–17h Attribute: R/W 427

- 40-43h Attribute: R/W, R/WC 429

- 44-47h Attribute: R/WO 429

- 60h Attribute: RO 429

- Register (USB xHCI—D20:F0) 430

- (USB xHCI—D20:F0) 431

- 80h Attribute: RO 432

- 81h Attribute: RO 432

- 82h-83h Attribute: RO, R/W 433

- 84h-87h Attribute: R/W, RO 433

- 88h-8Bh Attribute: R/W 433

- 8Ch-8Fh Attribute: R/W 433

- D4–D7h Attribute: RO, R/WLO 437

- D8h–dBh Attribute: RO, R/W 437

- DC–DFh Attribute: RO, R/W 437

- MaxPSASize+1 441

- Control USB2 Register 452

- Attribute: R/W,RO 453

- Attribute: RO 458

- Interrupter 459

- 1: Runtime Base + 28h–2Bh 460

- 1: Runtime Base + 30h–33h 460

- 1: Runtime Base + 34h–37h 461

- 1: Runtime Base + 38h–3Bh 461

- 11.3.4 Doorbell Registers 462

- SMBus Controller Registers 465

- (D31:F3) 465

- 0Ah Attributes: RO 467

- 0Bh Attributes: RO 467

- 10–13h Attributes: R/W, RO 467

- 14h–17h Attributes: R/W 468

- 20–23h Attribute: R/W, RO 468

- 2Eh–2Fh Attribute: R/WO 468

- Mapped I/O registers 469

- PEC_EN — R/W 471

- SMBus protocol 473

- SMB_BASE + 14h Attribute: RO 477

- SMB_BASE + 16h Attribute: RO 478

- SMB_BASE + 17h Attribute: RO 478

- PCI Express* Configuration 479

- Registers 479

- Mnemonic Register Name 480

- 00h–01h Attribute: RO 481

- F2/F3/F4/F5/F6/F7) 482

- F1/F2/F3/F4/F5/F6/F7) 485

- D28:F0/F1/F2/F3/F4/F5/F6/F7) 485

- PMLU32:PML 486

- 34h Attribute: RWO 487

- 3Eh–3Fh Attribute: R/W 487

- 80h–81h Attribute: RO 499

- 82–83h Attribute: R/W, RO 499

- 84h–87h Attribute: R/W 499

- 88h–89h Attribute: R/W 500

- 90h–91h Attribute: R/WO, RO 500

- 94h–97h Attribute: R/WO 500

- A0h–A1h Attribute: RO 500

- A2h–A3h Attribute: RO 501

- A4h–A7h Attribute: R/W, RO 501

- D4h–D7h Attribute: R/W, RO 502

- DCh–DFh Attribute: R/WC 504

- E1h Attribute: R/W 504

- ECh–EFh Attribute: R/W 504

- 10Ch–10Fh Attribute: RO, R/W 506

- 118h–11Bh Attribute: RO 508

- 320–323h Attribute: R/W 508

- 324h–327h Attribute: RO 509

- 330h–333h Attribute: RO, R/W 509

- High Precision Event Timer 511

- 00h Attribute: RO 512

- 010h Attribute: R/W 512

- 020h Attribute: R/WC 513

- Timer 0: 108h–10Fh 516

- Interrupt Rout Register 517

- Serial Peripheral Interface 519

- Configuration Registers) 522

- Section to observe 531

- Registers) 533

- 15.2 Flash Descriptor Records 535

- 15.3 OEM Section 535

- 16 Thermal Sensor Registers 545

- 16.1.3 CMD—Command Register 546

- 16.1.4 STS—Status Register 546

- 0Ch Attribute: RO 547

- 2Ch–2Dh Attribute: R/WO 549

- DWord Register 550

- (Thermal Sensor – D31:F26) 551

- TBARB+00h Attribute: RO 552

- T (offset 10h) 552

- TBARB+10h Attribute: RO, R/W 554

- TBARB+18h Attribute: R/W, RO 554

- TBARB+40h Attribute: RO, R/W 554

- Level Register 555

- TBARB+82h Attribute: RO, R/W 556

- TBARB+84h Attribute: RO, R/W 556

- 17 Intel 557

- Table 17-1. Intel 558

- MEI 1—D22:F0) 558

- Bus Master Enable (BME)— R/W 558

- 06h–07h Attribute: RO 559

- 10h–17h Attribute: R/W, RO 559

- 40h–43h Attribute: RO 560

- 17.1.1.14 ME_UMA—Intel 561

- 17.1.1.15 GMES—General Intel 562

- ME Status Register (Intel 562

- Command: Command code 563

- 60h–63h Attribute: RO 564

- 64h–67h Attribute: RO 564

- 68h–6Bh Attribute: RO 564

- 6Ch–6Fh Attribute: RO 564

- 70h–73h Attribute: R/W 564

- 74h–77h Attribute: R/W 565

- 8Ch-8Dh Attribute: RO 565

- 8Eh–8Fh Attribute: R/W, RO 565

- 90h–93h Attribute: R/W, RO 565

- 94h–97h Attribute: R/W 565

- 98h–99h Attribute: R/W 566

- A0h Attribute: R/W 566

- BCh–BFh Attribute: RO 566

- HER1: C0h–C3h Attribute: RO 566

- 17.1.2 MEI0_MBAR—Intel 567

- MEI 1 MMIO Registers 567

- MEI 2—D22:F2) 569

- Table 17-3. Intel 570

- MEI 2—D22:F1) 570

- 48h–4Bh Attribute: RO 573

- 4Ch–4Fh Attribute: R/W 573

- 50h–51h Attribute: RO 573

- 52h–53h Attribute: RO 573

- 17.2.2 MEI1_MBAR—Intel 576

- MEI 2 MMIO Registers 576

- 00–01h Attribute: RO 579

- 02–03h Attribute: RO 579

- 04–05h Attribute: RO, R/W 579

- 06–07h Attribute: RO 579

- 09–0Bh Attribute: RO 580

- 10–13h Attribute: RO, R/W 580

- 14–17h Attribute: RO, R/W 581

- 18–1Bh Attribute: RO, R/W 581

- 1C–1Fh Attribute: RO, R/W 581

- 20–23h Attribute: RO, R/W 581

- CA–CBh Attribute: RO 583

- CC-CFh Attribute: RO, R/W 583

- D0–D1h Attribute: RO 583

- D2–D3h Attribute: RO, R/W 584

- D4–D7h Attribute: R/W, RO 584

- D8–DBh Attribute: RO, R/W 584

- DC–DDh Attribute: R/W 584

- 17.3.2 IDER BAR0 Registers 585

- 01h Attribute: R/W 586

- 01h Attribute: R/W 586

- 02h Attribute: R/W 586

- 03h Attribute: R/W 587

- 04h Attribute: R/W 588

- 05h Attribute: R/W 589

- 06h Attribute: R/W 590

- 07h Attribute: R/W 591

- 17.3.3 IDER BAR1 Registers 592

- 17.3.4 IDER BAR4 Registers 593

- (IDER—D22:F2) 594

- 08h Attribute: R/W 596

- 09h Attribute: R/W 596

- 0Ah Attribute: R/W, RO 596

- 0Bh Attribute: R/W 596

- 0Dh Attribute: R/W 597

- 0Eh Attribute: R/W 597

- 0Fh Attribute: R/W 597

- Redirection (KT — D22:F3) 598

- 04–05h Attribute: RO, R/W 599

- 06–07h Attribute: RO 599

- 08h Attribute: RO 599

- 09–0Bh Attribute: RO 599

- 0Ch Attribute: RO 600

- 10–13h Attribute: RO, R/W 600

- 14–17h Attribute: RO, R/W 600

- 34h Attribute: RO 601

- 3C–3Dh Attribute: R/W, RO 601

- C8–C9h Attribute: RO 601

- CA–CBh Attribute: RO 601

- D0–D1h Attribute: RO 602

- D2–D3h Attribute: RO, R/W 602

- D4–D7h Attribute: RO, R/W 602

- D8–DBh Attribute: RO, R/W 602

- DC–DDh Attribute: R/W 603

- 00h Attribute: RO 603

- 00h Attribute: R/W 604

- 01h Attribute: R/W 604

- 02h Attribute: RO 605

- 02h Attribute: WO 605

- 03h Attribute: R/W 606

- 04h Attribute: R/W 606

- 05h Attribute: WO 606

- 06h Attribute: RO 607

(4 paginas)

(4 paginas) (74 paginas)

(74 paginas)

Comentarios a estos manuales